现代计算机主内存的简单原理(DDR5为例)

原视频(B站):https://www.bilibili.com/video/BV1vP411c7pt?vd_source=2def051c1c2e4e1a3cd81c5ac9e028e4

原视频(油管):https://www.youtube.com/watch?v=7J7X7aZvMXQ

首先,计算机主板上有4个DIMM插槽,一个DIMM(内存条)上有8个DRAM芯片。DRAM通过双内存通道直接连接CPU,CPU中的内存控制器进行与内存的通信和管理。而M2/SATA等硬盘,则有单独一部分元件与其进行通信。CPU管理着SSD、缓存、DRAM之间的数据流。内存的供电是由主板提供的,DDR5上存在电源管理芯片。

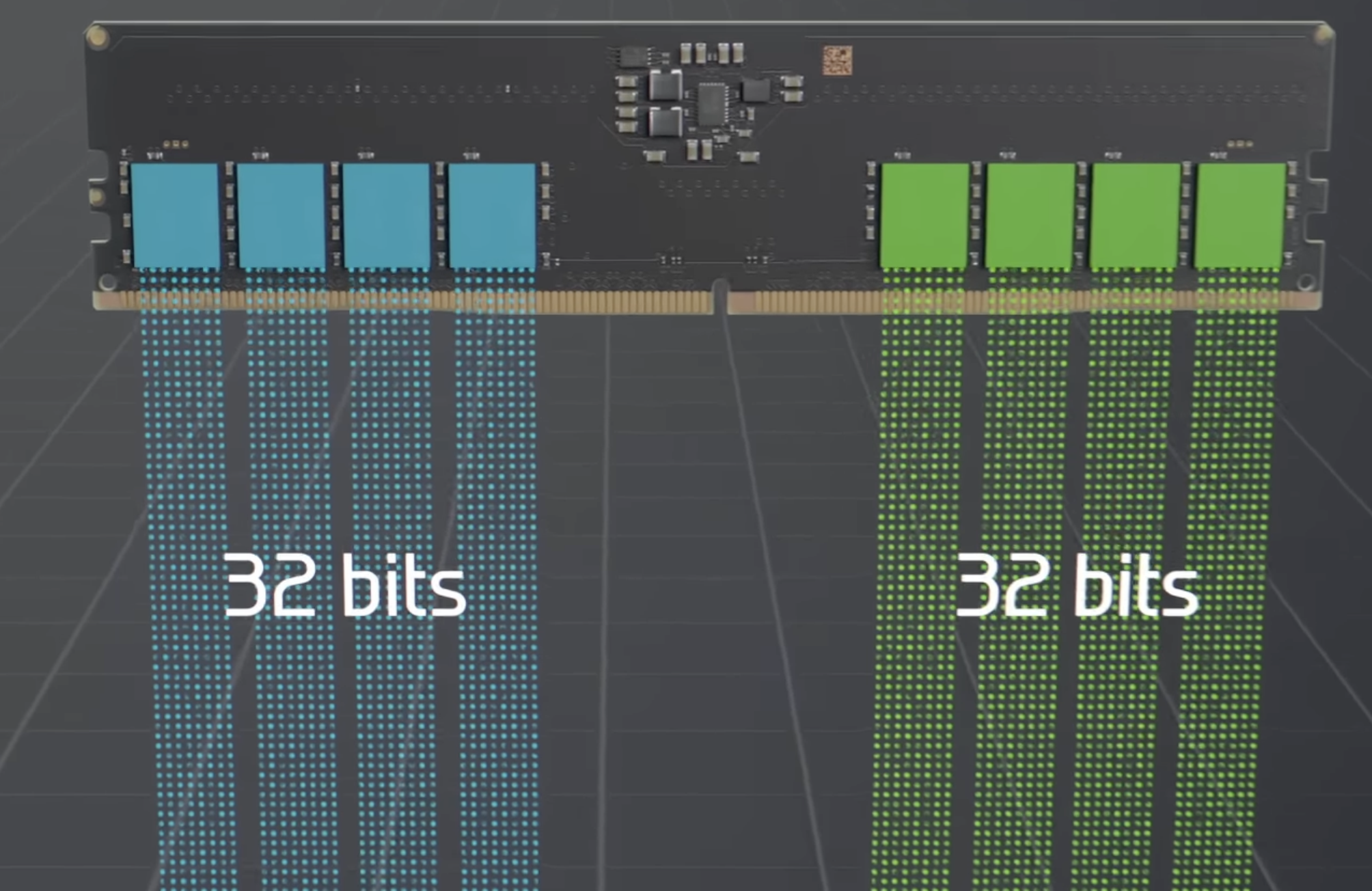

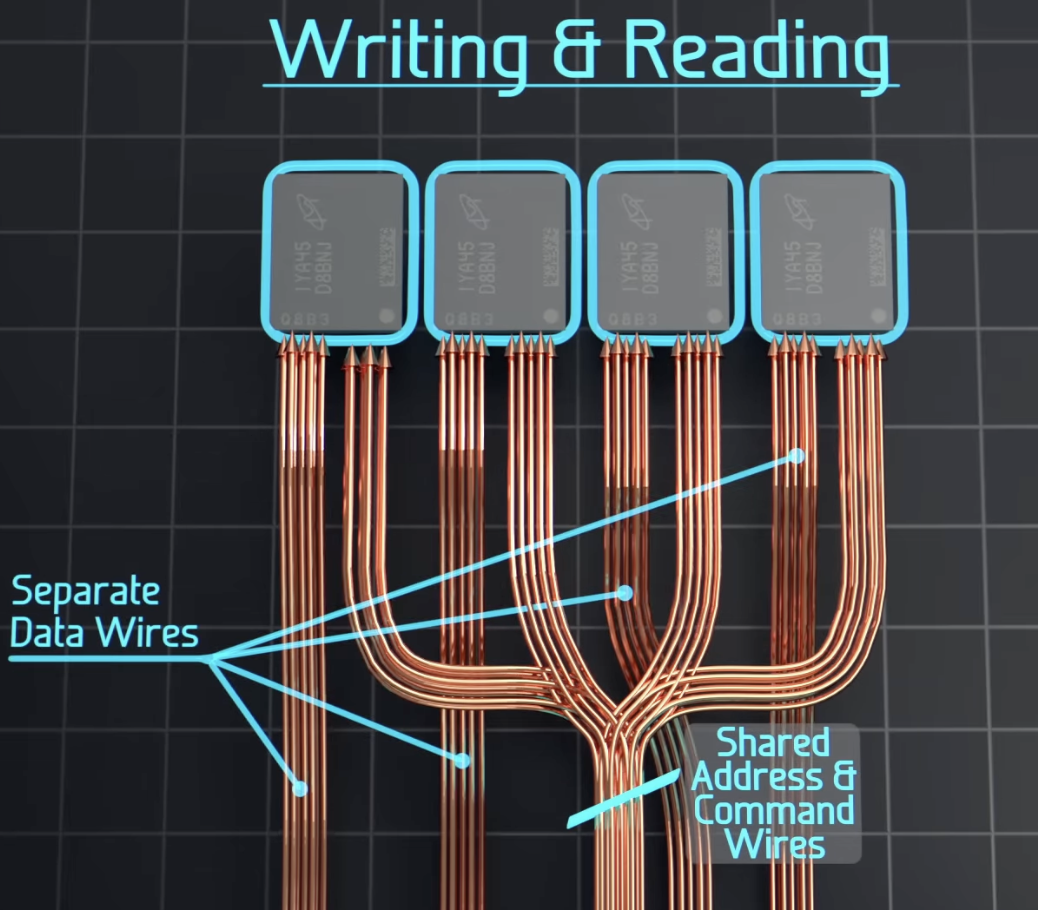

在DDR5 中,分为2个通道。这2个通道使用32条数据导线一次独立传输32位。通过使用21根额外的导线,每个内存通道携带一个用于指定读取或者写入数据位置的地址,使用7跟控制信号线转发命令。地址和命令将被发送并共享到内存通道上的4个芯片(双通道,一边各四个)。32位数据传输到4个DRAM上,每个DRAM只能一次读写8位。

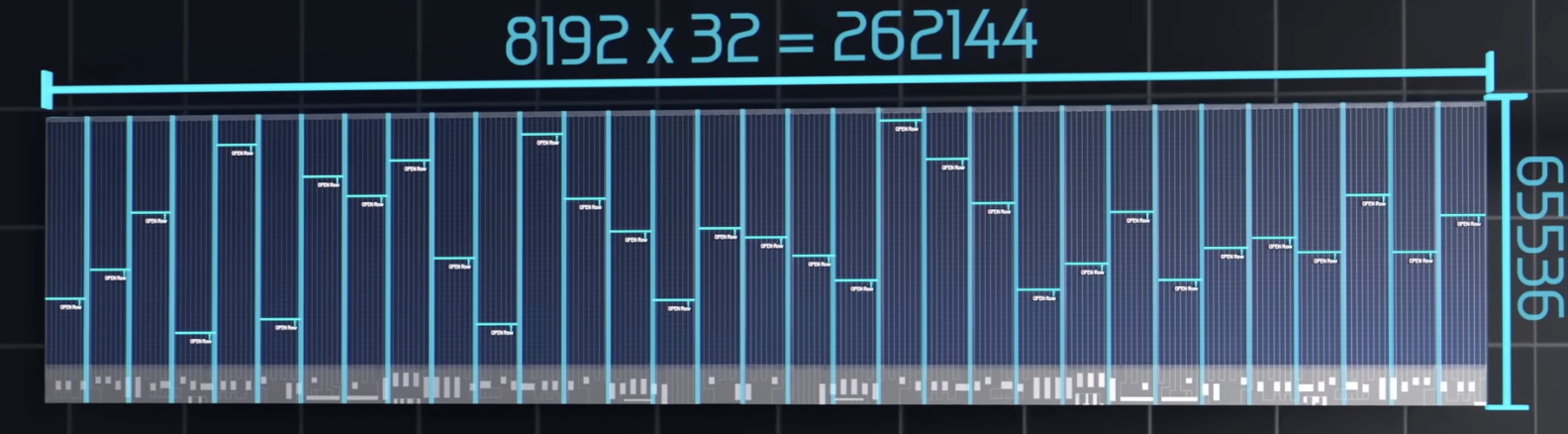

DDR5的外部包装中,是由底部的球栅阵列和芯片连接起来的互连矩阵。一块16GB的内存上,每个DRAM芯片大小为2GB,即2千兆字节。每个芯片可分成8个“库组-bank group“,每组由4个库组成,一共32个库。每个库内都有一个巨大的阵列,高65536个存储单元、列8192个单元。库的行列之间有数万条导线以及各组外围的支持电路来支撑工作。

计算可知,每块DRAM芯片上一共有65536 * 8192 * 32 = 170亿个存储单元。为了快速访问,需要一个31位的地址。例如:0111001100011010111001001000011。即:

3位选择库组+2位选择库+16位行地址[6.5万行中的某行]+10位列地址[8192列中的某列]

这31位地址被分成2部分,使用21条导线来分别发送。16 + (2+3=5)& 10

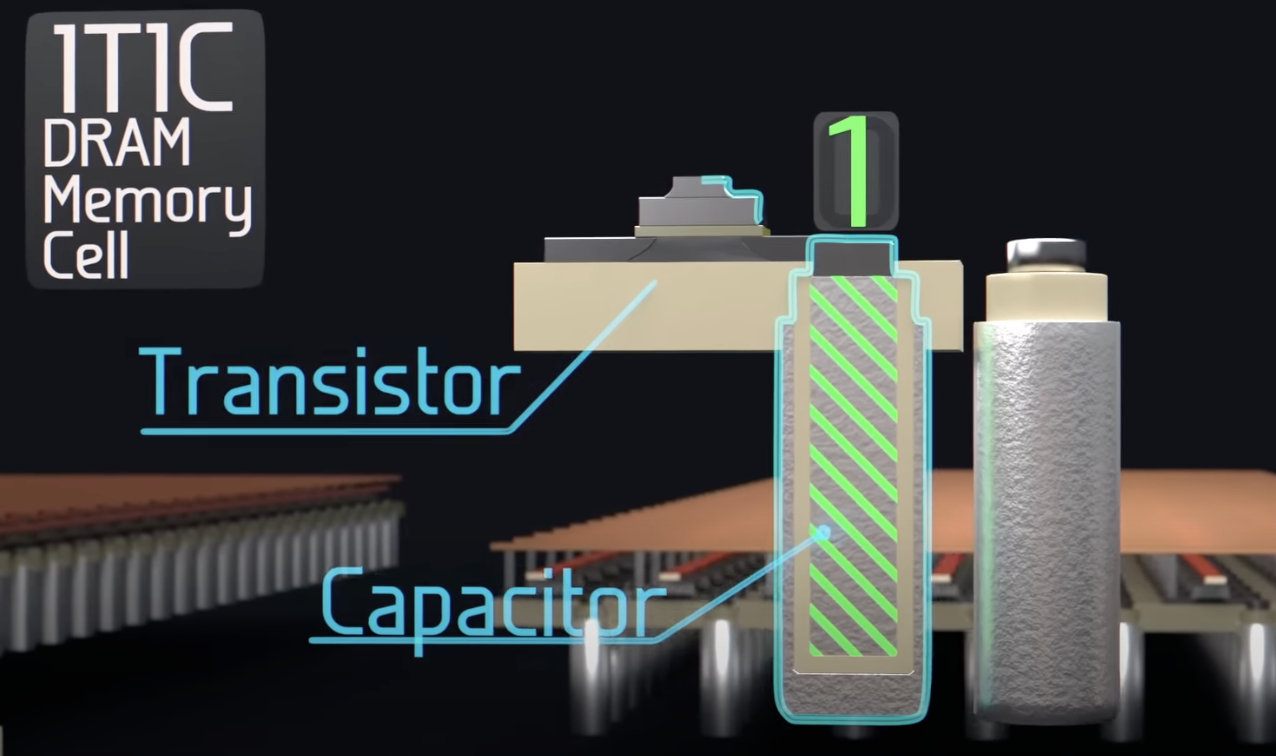

单个存储单元的物理结构

这些芯片又称集成电路,是在直径300毫米的硅晶圆上制造的。每片硅晶圆上游2500个左右裸芯片。每个裸芯片上游数十亿纳米级的存储单元,通过几十种步骤和工具从半导体制造厂或Fab(圆晶厂)中制造出来。

DDR5中的存储单元,被称为1T1C单元(1T1C DRAM Memory Cell),大小为几十纳米,分为2个部分:

1、电容器

以电荷或电子的形式存储1bit的数据。电容器的形状像一个挖在硅上的深沟,由2个导电表面组成,中间有一个只有几原子厚的绝缘体,绝缘体可以阻止电子流动,但允许电场通过。如果这个电容器被电子充电到1v,那么它就是二进制的1 ;如果没有电荷,处于0v,则为二进制的0。因此一个单元只容纳1bit数据。(沟槽式电容器中,硅的深度用于增加更大的电容存储)

2、晶体管

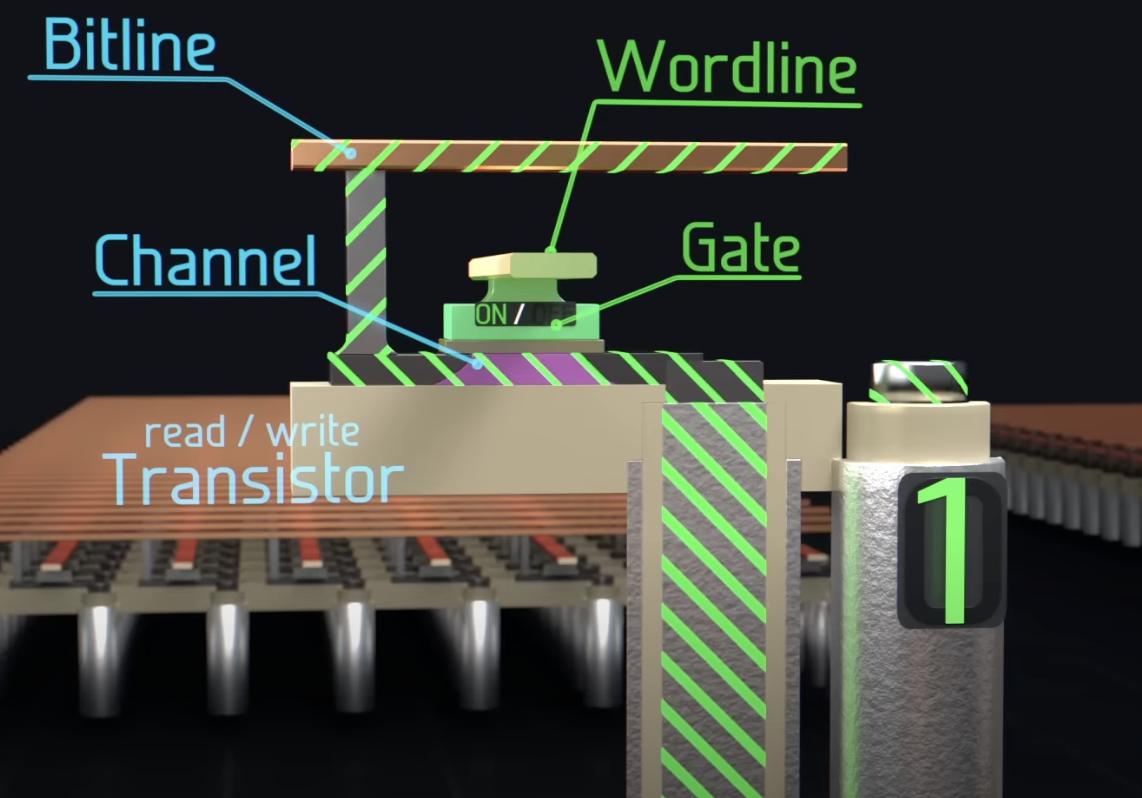

用于读取或存储数据,晶体管连接着2根导线:

- 字节线(字线-wordline)连接晶体管的栅极

- 比特线(位线-bitline)连接晶体管的另一侧

在字线上施加电压可使晶体管导通,字线开启时,电子流过通道,将电容器连接到位线。这样就可以进入该存储单元并给电容充电写下1;当字线关闭时,晶体管也随着关闭,电容放电写0。当电容器与位线隔离,从而保存了之前写入的数据或电荷。由于晶体管很小,电子会慢慢在通道上泄漏。因此随着时间的推移,电容器需要被刷新,以便为泄漏的电子充电。

(外部通过测量电荷量来读取电容器中的存储值)

库的解析

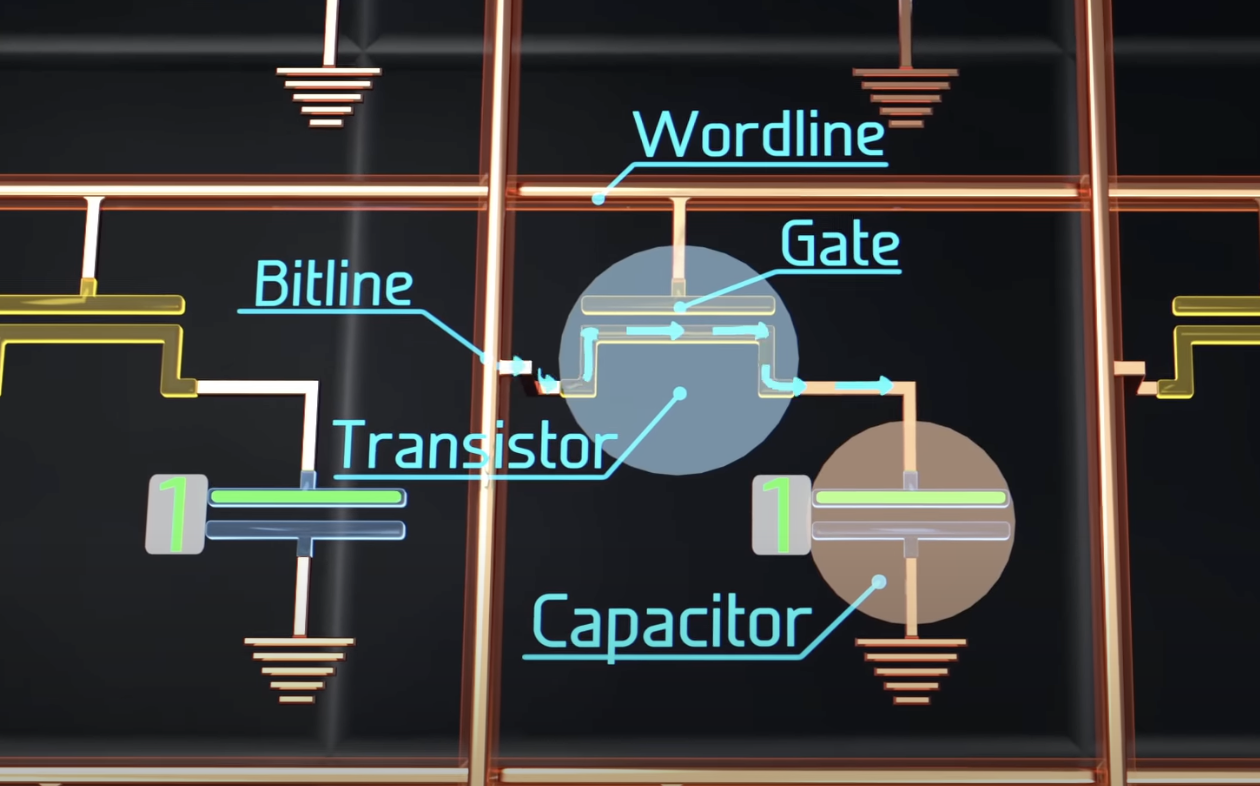

假设有一个由数量较少存储单元组成的小型阵列。该阵列的每条字线都是按行连接,位线按列连接。字线与位线在不同的垂直层,因此位线跨越在字线上,并不相交。字线按行连接每个晶体管的控制栅,位线按列连接每个电容器对面的通道。

当1个字线被激活时,只有该行的所有电容器连接到相应的位线,从而激活了该行所有的存储单元。在任何时候都只有一条字线处于激活状态。如果一列中的多个电容器被连接到位线上,电容器的数据存储功能会相互干扰。

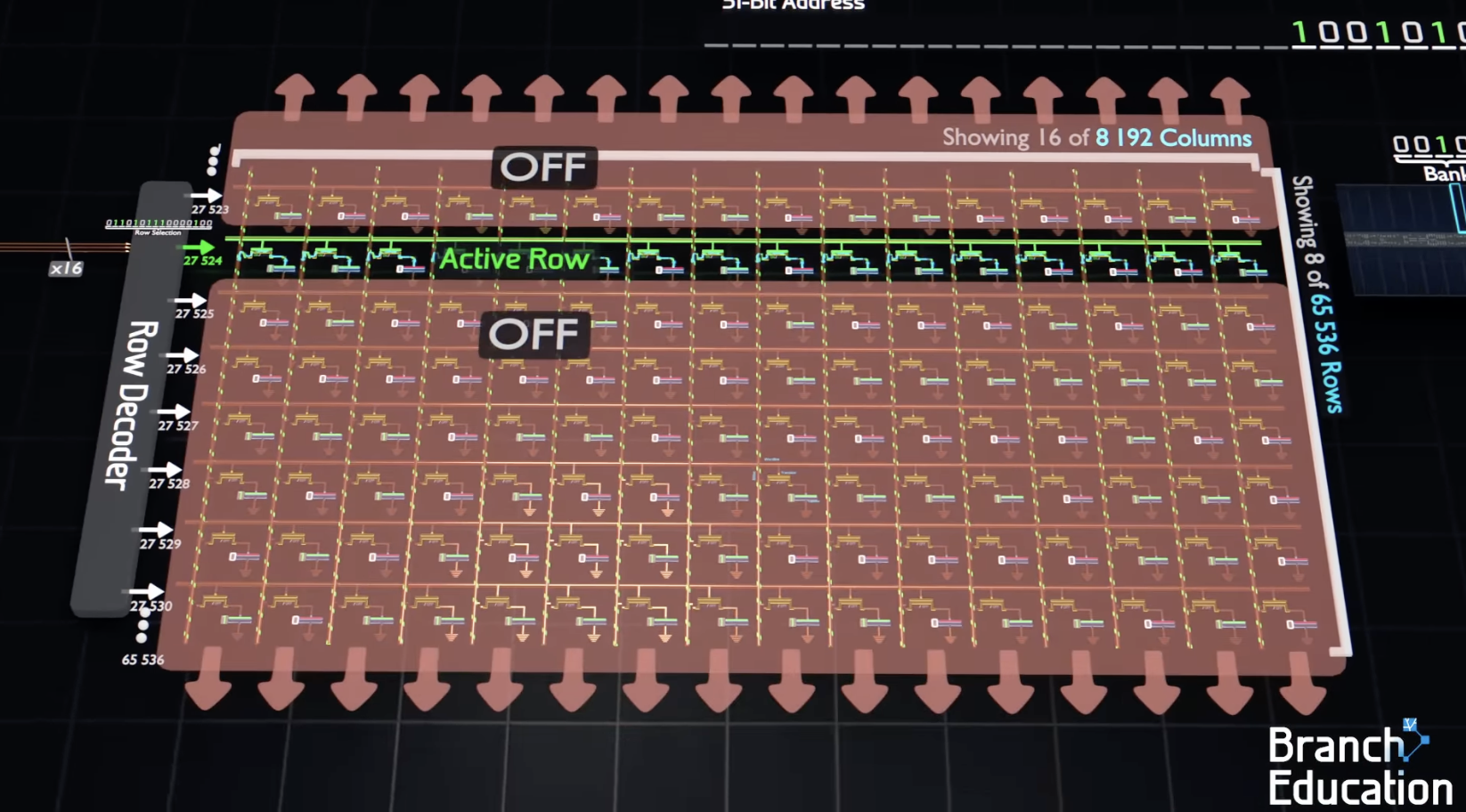

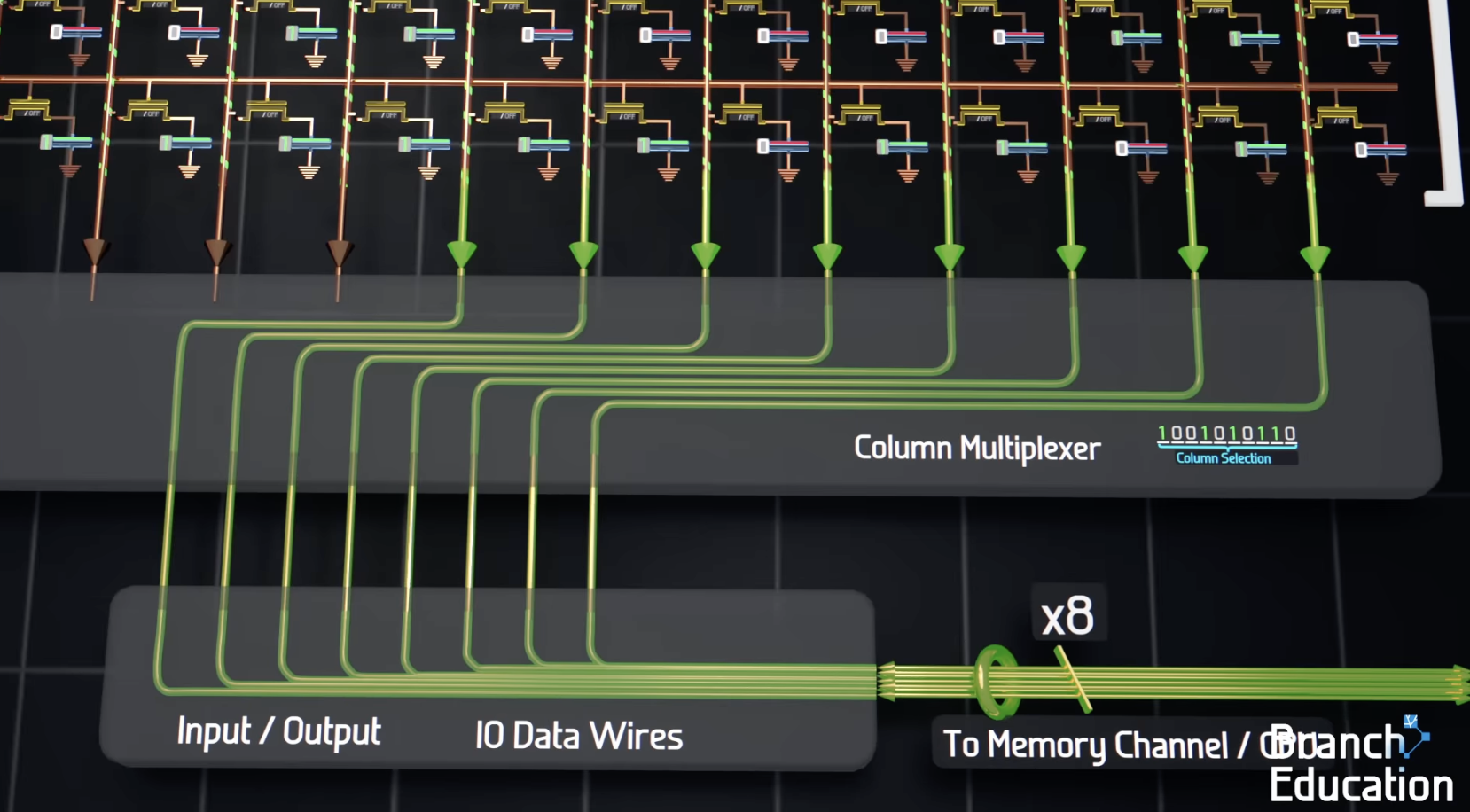

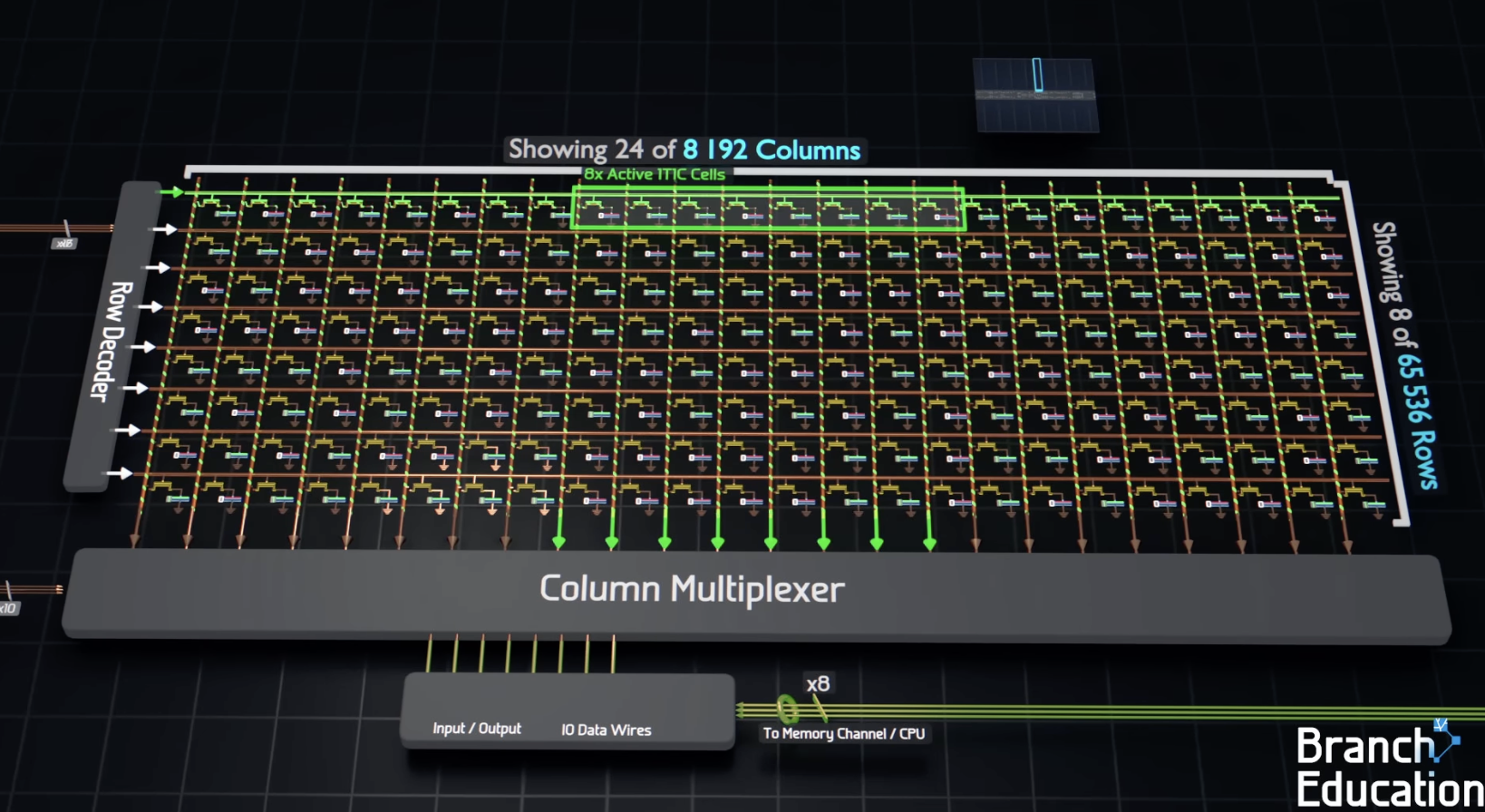

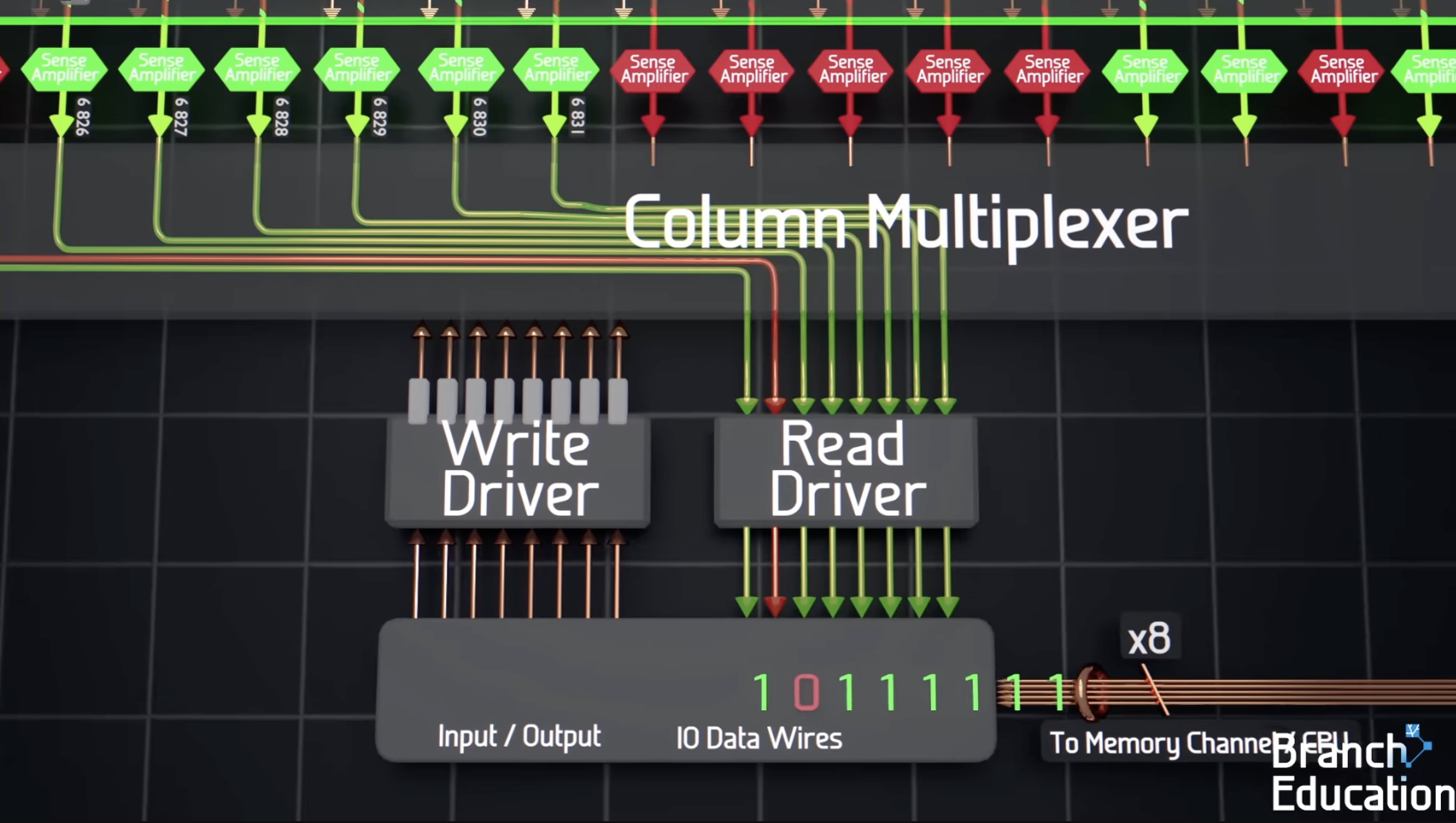

一个库内有65536行和8192列,31位地址是用来激活一组仅有的8个存储单元。前5位选择库组-库;中间16位发送到行解码器以激活指定行,找到该行后,会将该行开启并将8192个电容器连接到对应的位线上。当前行开启时,其他条字线全部处于关闭状态;末尾10位发送到列复用器,库的下方是一个多路复用器,接收顶部的8192条位线,并根据10位的地址,将一组特定的8位线连接到底部的8个输入和输出I/O线。例如10位地址1001010110,那么只有第4784到4791条位线会被连接到I/O线,其余8000多位线不会被连接到任何东西上。

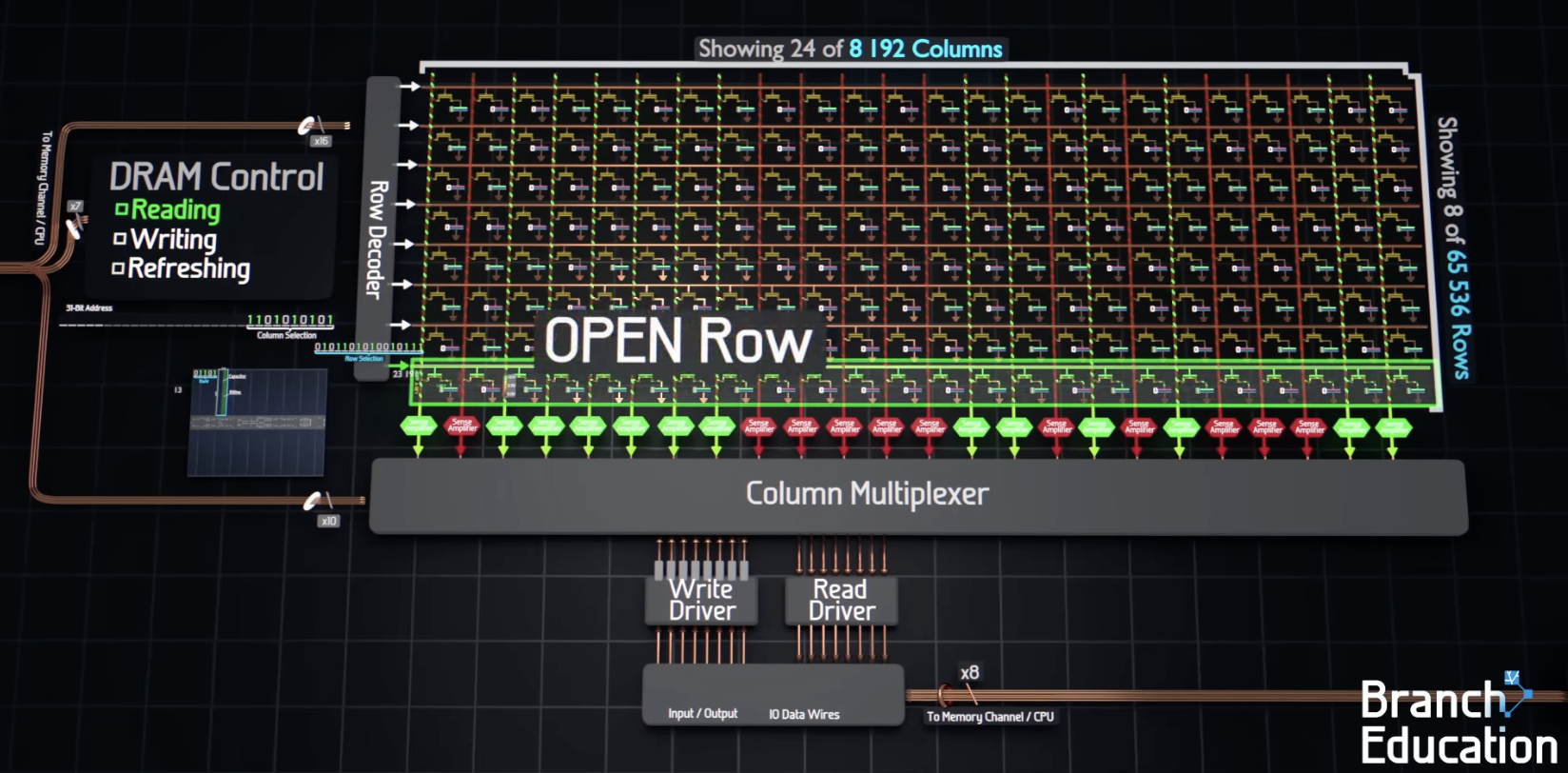

通过这种方式,就可以访问这个大规模阵列中任何存储单元。在这个阵列中每个位线的底部,都有一个电流感应放大器、列复用外的读写驱动器。

对存储单元的读、写、刷新

读取

CPU发送读取命令和31位地址到DRAM,DRAM根据前5位选中某个库,然后关闭所有字线,隔离所有电容。并将所有8000左右的位线预充电到0.5V。

然后根据16位行地址打开某行,该行所有电容都会被连接到他们的位线上。如果一个单独的电容器持有1,并被充电到1V,那么一些电荷就会从电容流向0.5V的位线上,位线上的电压就会增加。感应放大器能检测到位线上电压这种细微变化,并放大这一变化,再讲位线上的电压一直推高到1V。

如果电容中存储了0,电荷就会从位线流向电容,0.5V的比特线的电压就会下降,放大器感应到并放大,再驱动位线电压下降到0V或接地。

感应放大器:由于电容器很小,位线很长,电容器需要一个额外的组件来感应和放大所存储的任何数值

列选择复用器使用10位列地址连接相应的8个位线到读取驱动器。驱动器通过8条数据导线将这8个值和电压发送给CPU。

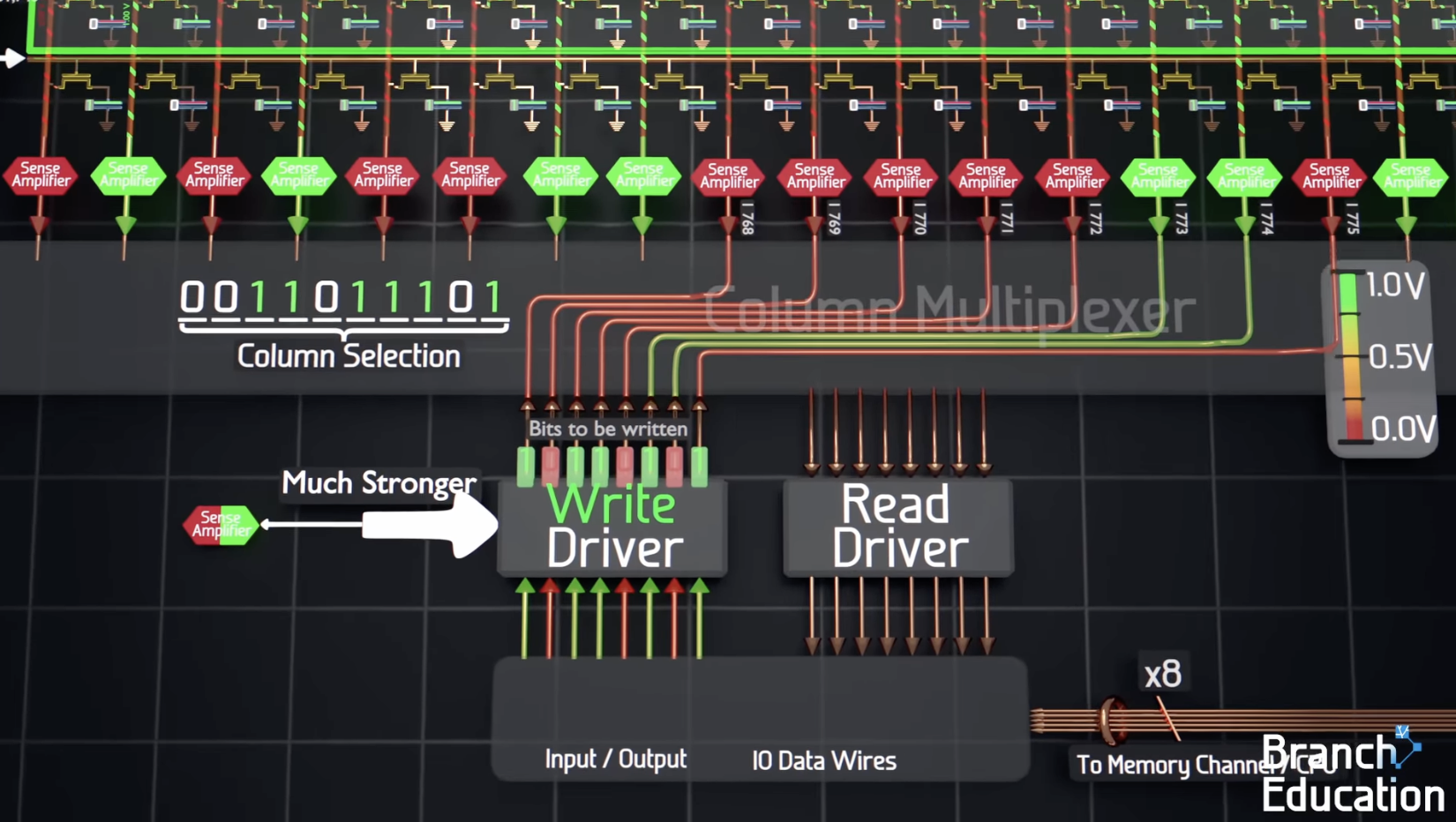

写入

首先,写入命令、地址和要写入的8位被发送到DRAM芯片,然后与读取一样,选中库、隔离电容、位线预充电、通过16位行地址激活单行,电容会干扰比特线的电压取值,感应器放大信号并驱动位线电压为1或0。然后列地址进入多路复用器,由于发送了写命令, 多路复用器将特定的8位连接到写入驱动器,驱动器包含了CPU沿着数据导线发送并要求写入的8个位。写入驱动器比感应放大器强很多,因此可以覆盖之前在位线上的任何电压值,并将8个位线中的每一个值写入,1V写1,0V写0,这样就将8位数据写入到31位地址相对应的存储单元中。

注意:

1、读写时,同一个通道内的所有4个芯片是同时进行的,4个芯片使用相同的31位地址和命令线,但每个芯片都有不用的数据导线。

2、DDR5中的二进制1电压实际上是1.1V,前几代内存的电压甚至更高,当位线预充电时,是实际电压的一半,例如DDR5是0.55V。在实际写入或刷新时,施加存储到电容器的电压大概是1.4V,因为电荷会随着时间推移而泄漏。但为了便于理解,仍然使用0和1描述。

3、库、库组、位线、字线的数量,不同世代和容量之间有很大不同,但他们总是2的n次幂。

刷新

由于隔离电容器的晶体管非常小,因此电荷会在通道上泄漏。刷新的操作很简单,先关闭所有行,将位线预充电到0.5V,然后打开一整行。跟之前一样,电容扰动位线,感应放大器驱动位线和电容的电压到开放的行上,取决于电容器的存储值,将其完全上升至1V或0V,达到重新填充泄漏的电荷的效果。这个【关闭行、预充电、打开行、感应放大】的过程,需要一行一行地做,每行花费50ns,65536行轮流刷新一次需要3ms左右,每个库的刷新频率是每64ms一次。因为64ms低于一个存储单元需要的由于泄漏过多的电荷使得存储的1变成0而导致数据丢失的最短时间。

DRAM存储单元处理的数据量相当庞大,每秒需处理48亿个读写数据的请求,同事要把每行的每个存储单元每秒逐行刷新16次,内存做的是一些简单的事情,例如对比、计算和移动数据,但它的速度是每秒数十亿次。这些功能让计算机得以实现运行例如大型游戏等应用。游戏中的道具和画面需要计算,还有各个独立的物体,他们的位置和形状被存储在DRAM中;还有环境的照明、颜色、纹理的改变等等,都需要做大量的计算。

为什么要有32个库

当某一个库的某一行被打开时,只需使用10位列地址和列选择复用器,就可以读取或写入8个存储单元的任何部分。CPU向某行发送读写命令被称为行命中,行命中会持续不断发生,行命中,时,会跳过所有打开行的步骤,并只用10位列地址来复用一组不同的8列或位线,将其连接到读取或写入驱动器上,从而节省了不少时间。(没懂为什么节省时间)

行错过是指下一个地址是针对不同行的情况,这需要DRAM关闭并隔离当前打开的行,再重新打开新的行。在DRAM包装上,一般有4个数字用于说明关于行命中、预充电和行错过的时间等相关参数。(如下时间以时钟周期为单位测量)

1、 40 CAS Latency :延迟,指发送一个打开了的行的内存地址起(即行命中),到接收到存储在这些列中的数据的时间。

2、39 RAS to CAS Delay tRCD:是在所有行都被隔离并且位线被预充电的情况,打开一个行所需的时间。

3、39 Precharge tRP:打开一行之前对位线进行预充电所需的时间。

4、79 Activate Precherge Delay [tRAS] :激活一行和接下来的预充电之间所需的时间。

行命中也是地址分两部分发送的原因,寿险是RAS(行地址选通)的库选择和行地址,然后是称为CAS的列地址选通,如果第一部分库地址和行地址与当前打开的行一样,就是行命中的情况,DRAM只需要列地址和新命令,多路复用器就会在开放行周围移动。由于访问开放行可以节省时间,CPU的内存控制器、程序和编译器,都是向增加后续行命中的数量这个思路去优化的。

与行命中相反的是抖动,当一个程序一次又一次从一行跳到另一行,在能源和时间方面是非常低效的。DDR5 有32个库,每个库的行、列、感应放大器和航解码器都是相互独立运行的,因此来自不同库的多个行可以同时被打开,以增加行命中的可能性,减少CPU访问数据的平均时间。通过多个库组,CPU可以一次刷新一个库组的一个库,同时还能使用其他 3 个库,从而减少刷新的影响。

一个库的高度为65536,宽度为9192。将所有的库一个个连在一起,可以任务这个芯片实际上有6.5万高,26.2万列宽,在列之间添加31个等距分割点,就分出来一个个库。从而在读写和刷新方面更高效灵活。

DRAM上的容量单位:GB

16GB:16吉字节

48000 Million Transfers per Second:每秒传输以百万为单位的数量

38400 Peak Megabytes per Second:以兆字节每秒为单位的峰值数据传输率

突发缓冲器和突发长度

突发缓冲器是一个128位的读写临时存储位置,多路复用器中接出来是8条导线,突发缓冲器有128条导线接到128位的缓冲区。10位的列地址会被分解为两部分:6比特用于多路复用器,4比特用于突发缓冲器。

例如一个读取命令,128个存储单元和位线将使用6个列的位连接到突发缓冲器上,从而临时加载或缓存128个值到突发缓冲区,通过使用缓冲区的4位,突发缓冲区中的8个快速访问的数据位置被连接到读取驱动器上,通过循环使用这4位,所有16组8位都能被读出。因此其突发长度为16。之后,一组新的128位线和数值被连接并加载到突发缓冲器中。写操作也是类似的。

突发缓冲器中每个微芯片中16组8位,总共1024位数据,只要这些数据是相邻的,就可以极快地被访问、读写。但是如果数据请求跳来跳去,也仍然有粒度和能力来访问任何一组8位数据。